Help! I need to create symbols for a Xilinx® Ultrascale Plus XCVU19P FPGA

This device has 3824 pins. My boss told me I have one day to complete this task, and the engineer who wants these symbols is very picky.

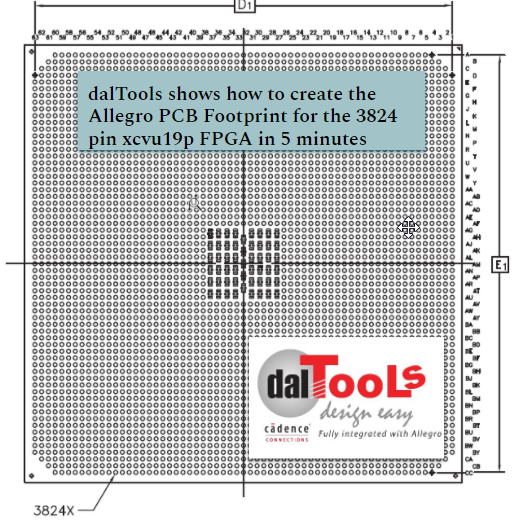

The pin-counts for high end FPGA devices are exploding. Xilinx® has just released 2 variants of the xcvu19p UltraScale Plus® FPGA device in a 3824 pin package, their largest device/package to date. They also offer many variations of devices in 2500+ pin packages.

How can an engineer or symbol Librarian be expected to accurately build, modify and maintain symbols for devices of this size on such tight schedules?

Exploding Pin Counts!

spend an Hour with PartBuilder and Take the Rest of the DAY off

PartBuilder builds flexible/functional schematic symbols for any size FPGA device from Intel®/Altera®, Lattice®, MicroChip®/MicroSemi® and Xilinx® in less than an hour. Typical creation times for experienced users are much shorter, especially if the user has already created symbols for another FPGA in the same device family.

PartBuilder creates the symbols for Allegro-HDL®, Altium®, Mentor dxDesigner® and Pads-Professional®, Orcad-Capture®, and Zuken® tools.

Most importantly PartBuilder can be easily configured to build symbols meeting your exacting Library Standards.

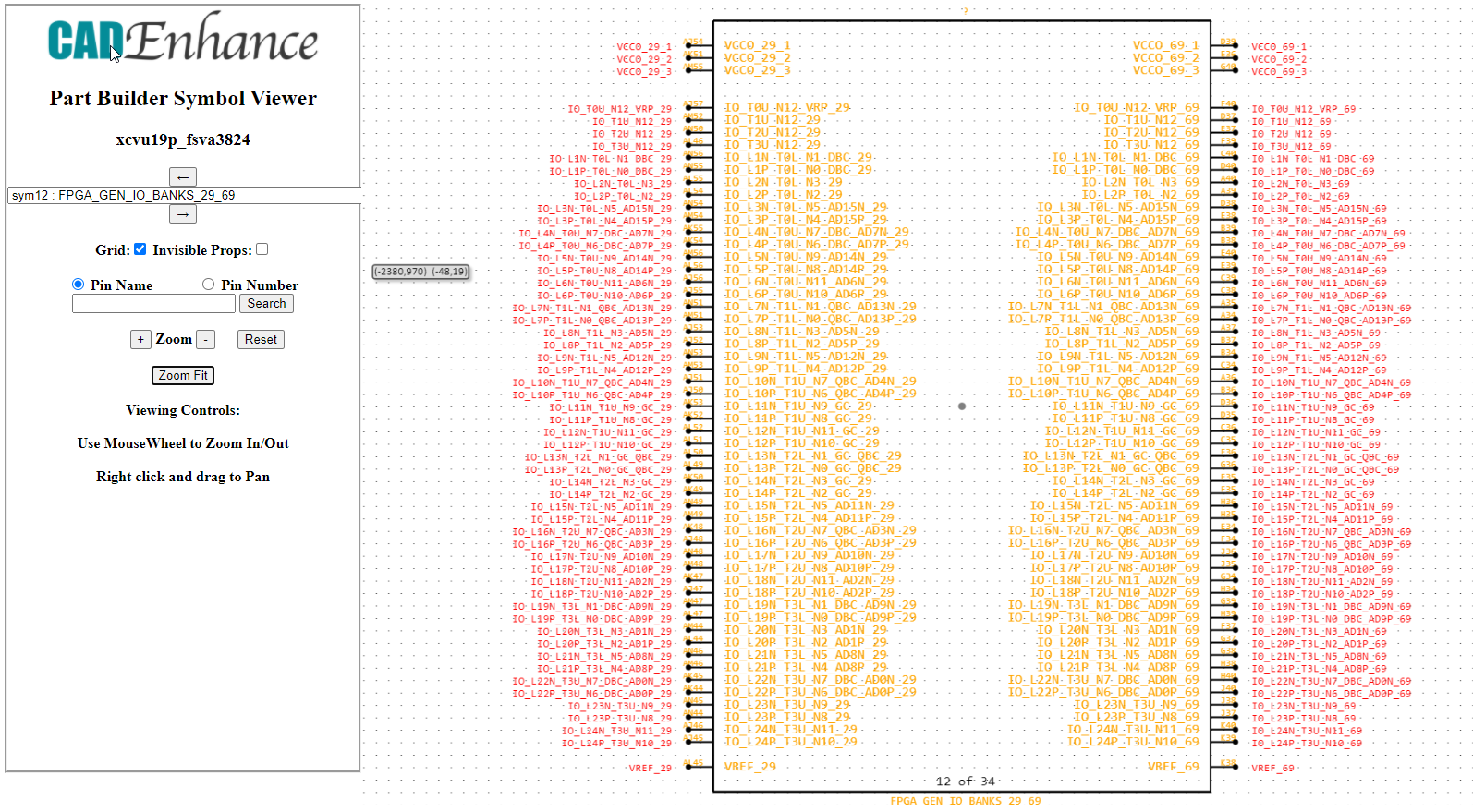

With very little setup, PartBuilder will create 66 functional Symbols for the xcvu19p-fsva3824 for your schematic tool in less than 15 Minutes.

CAn I reduce the Symbol Count To something more Manageable for the Schematic?

In under an hour you can customize the FPGA symbols for this giant device to meet the demands of the pickiest Engineer (who might even be you!)

In the video playlist below, we show the detailed steps you can take to get more control over the final symbol set that you will release into your library.

We demonstrate how to use the Symbol Description Language (SDL) REPLICATE Loop to duplicate a template symbol with 2 Full IO banks

Following that, We create another template symbol with 3 full High Speed transceiver banks and add a loop that creates 4 symbols housing all of the High Speed transceiver pins.

Once you create these template symbols, you can apply them to any other device in the Xilinx Ultrascale and Ultrascale Plus families, saving even more time and producing consistent library symbols that make it easy to replace one FPGA for another in your schematics. To build a different FPGA in the same family, you’ll only need to change the REPLICATE loop parameters to capture the different number of Generic I/O banks and XCVR I/O banks.

DEtailed Video

How about the PCB FootPrint?

WRapping It All UP

Sign up for a demo with one of our experts today and you’ll get access to the symbols we created in the demo video. You’ll also be able to use our complete tool free for 1 month to customize the symbols to your needs.

When you download the tool you also get the FREE AllegroHDL, Orcad and Mentor Symbol viewer providing easy access to part and pin properties and powerful Pin Name and Pin Number searches across symbols not seen in the standard EDA vendor tool sets.

PartBuilder from CadEnhance automates the creation of FPGA symbols for devices with 50 to 5000+ Pins. Symbols for any size device can be easily created in less than an hour.

PartBuilder uses built in FPGA intelligence to quickly and accurately divide these parts into interchangeable functional symbol blocks making it easy to work with in the schematic. The Symbol Description Language (SDL) enables easy manipulation to create the final symbol set you need, instead of forcing you to use one generic solution.

Just as important, the symbols are built using your exacting library standards with fully programmable property content and locations.

Thanks to the automation, PartBuilder can extract and add important additional pin-attributes including pin-delay and diff-pair identification that most symbol libraries are lacking today due to the daunting nature of the task.