Your EDA Tools…. Our Automation

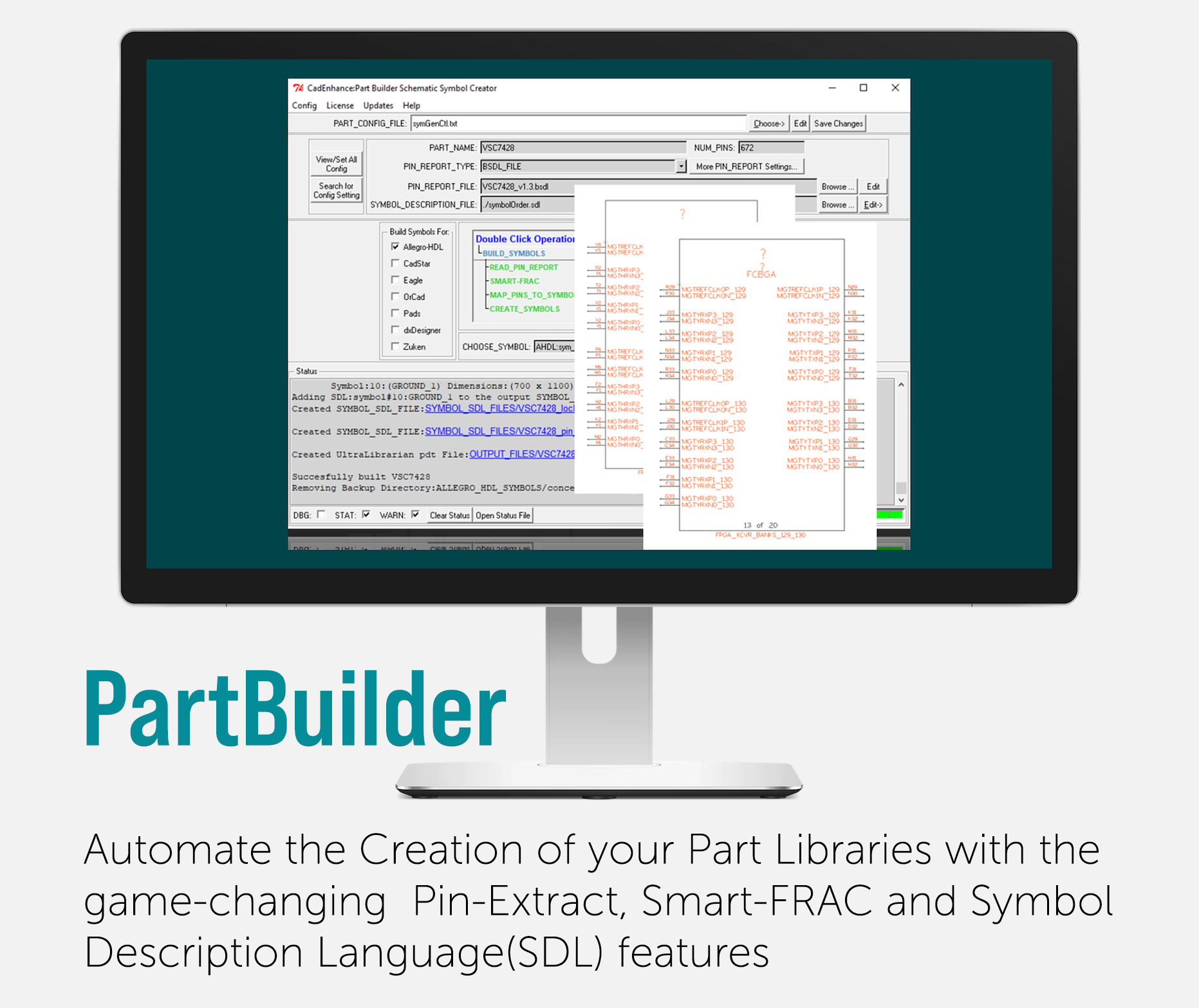

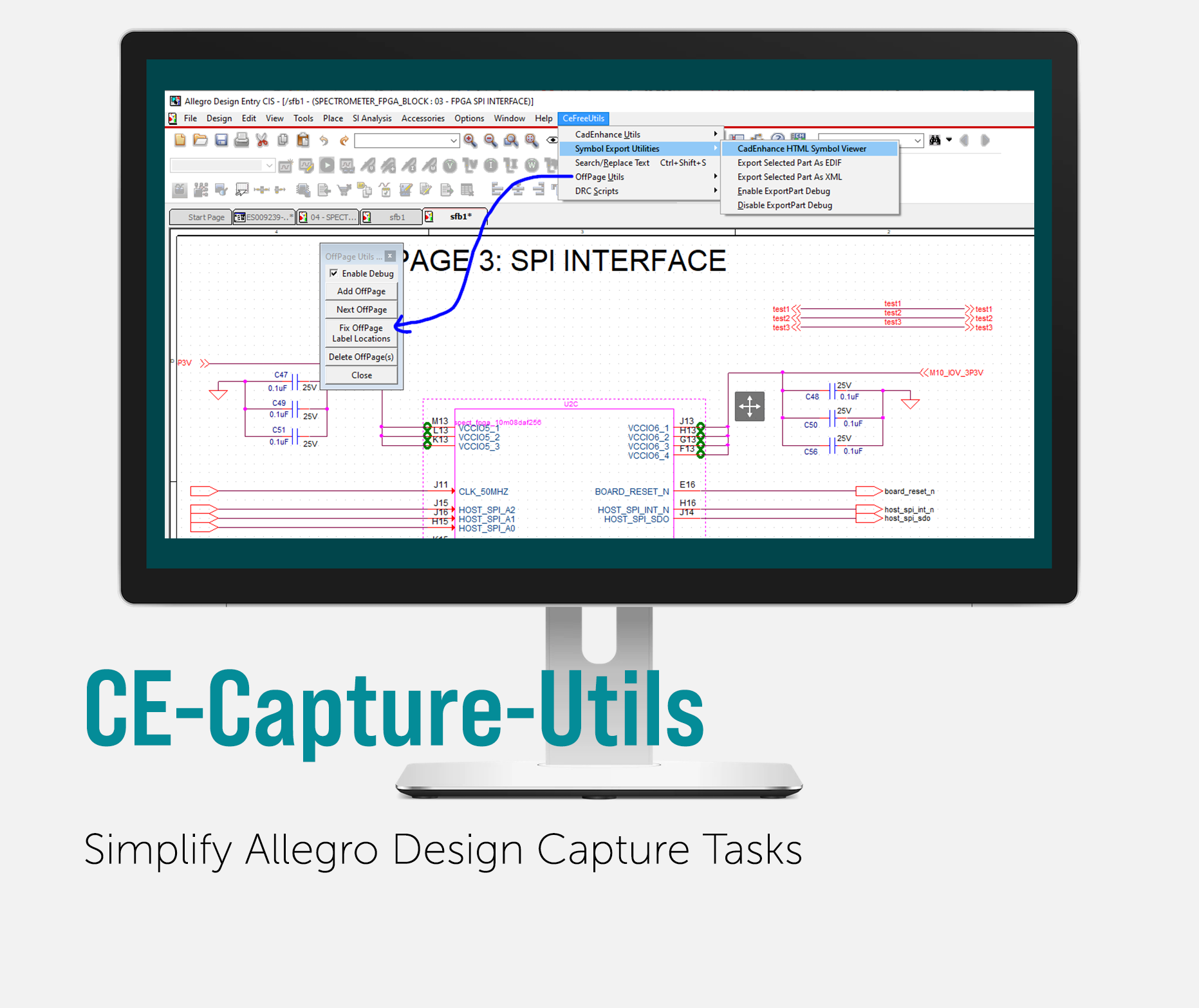

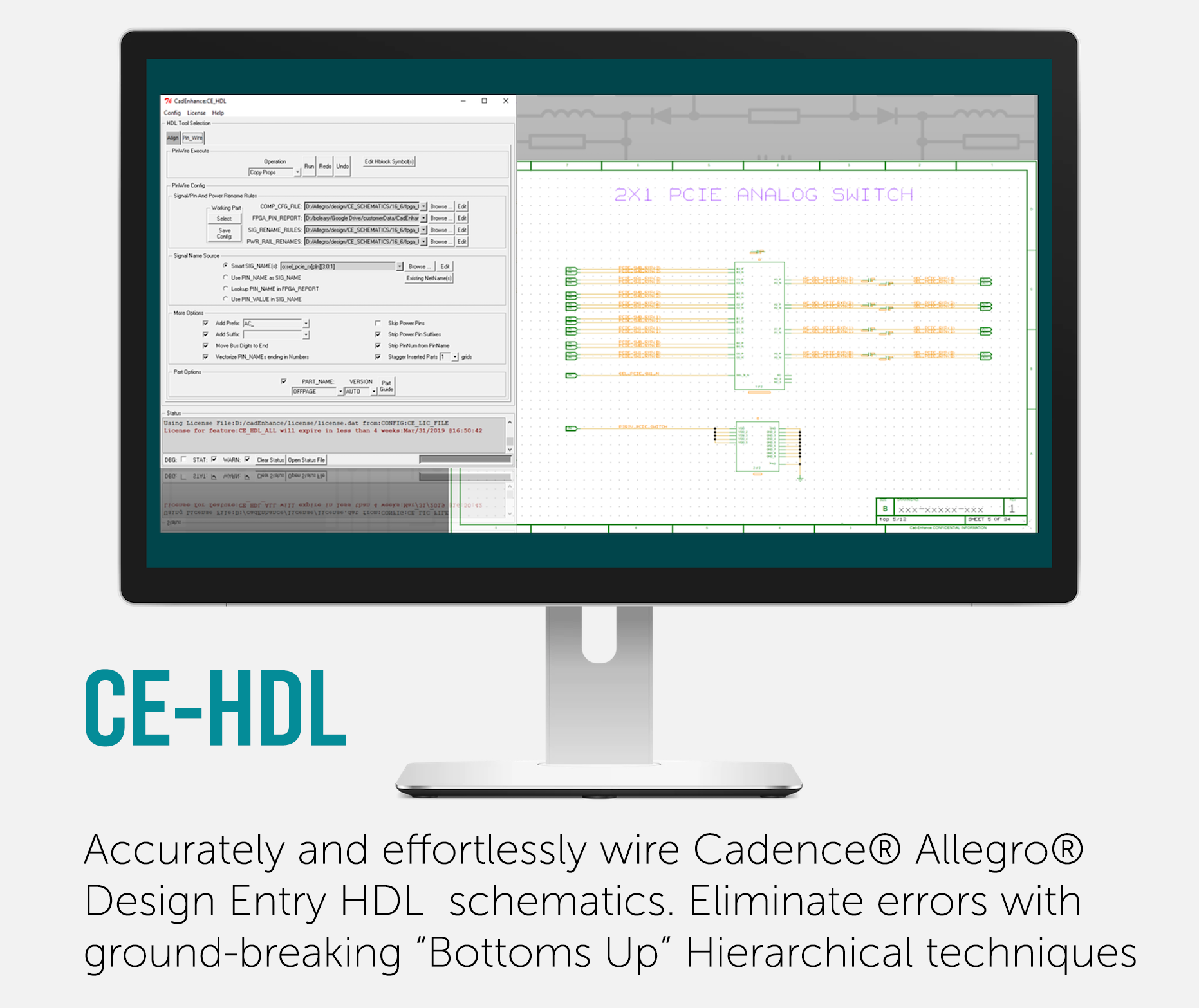

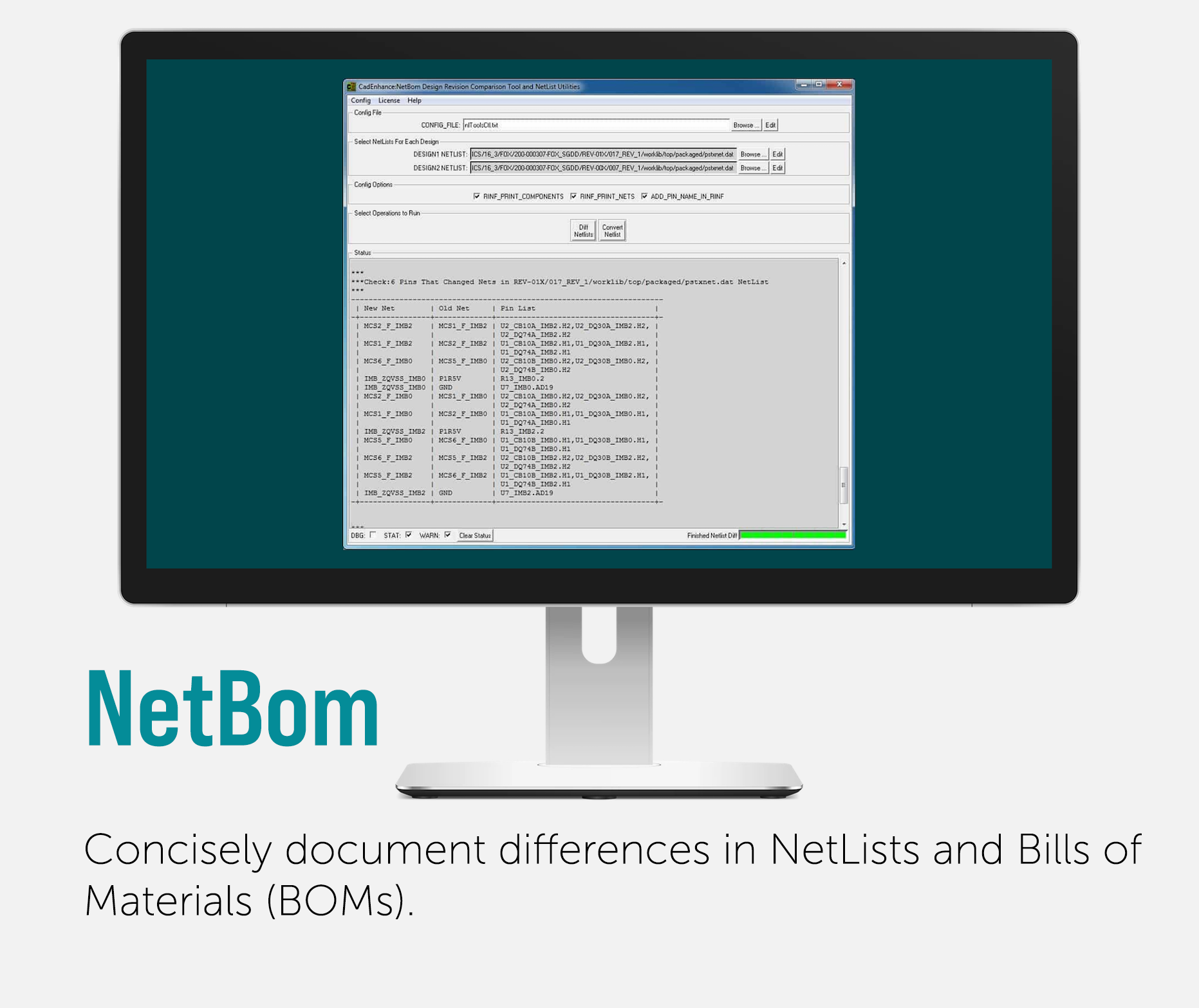

CadEnhance provides software tools and services to improve the hardware design process for electrical engineers and printed circuit board designers

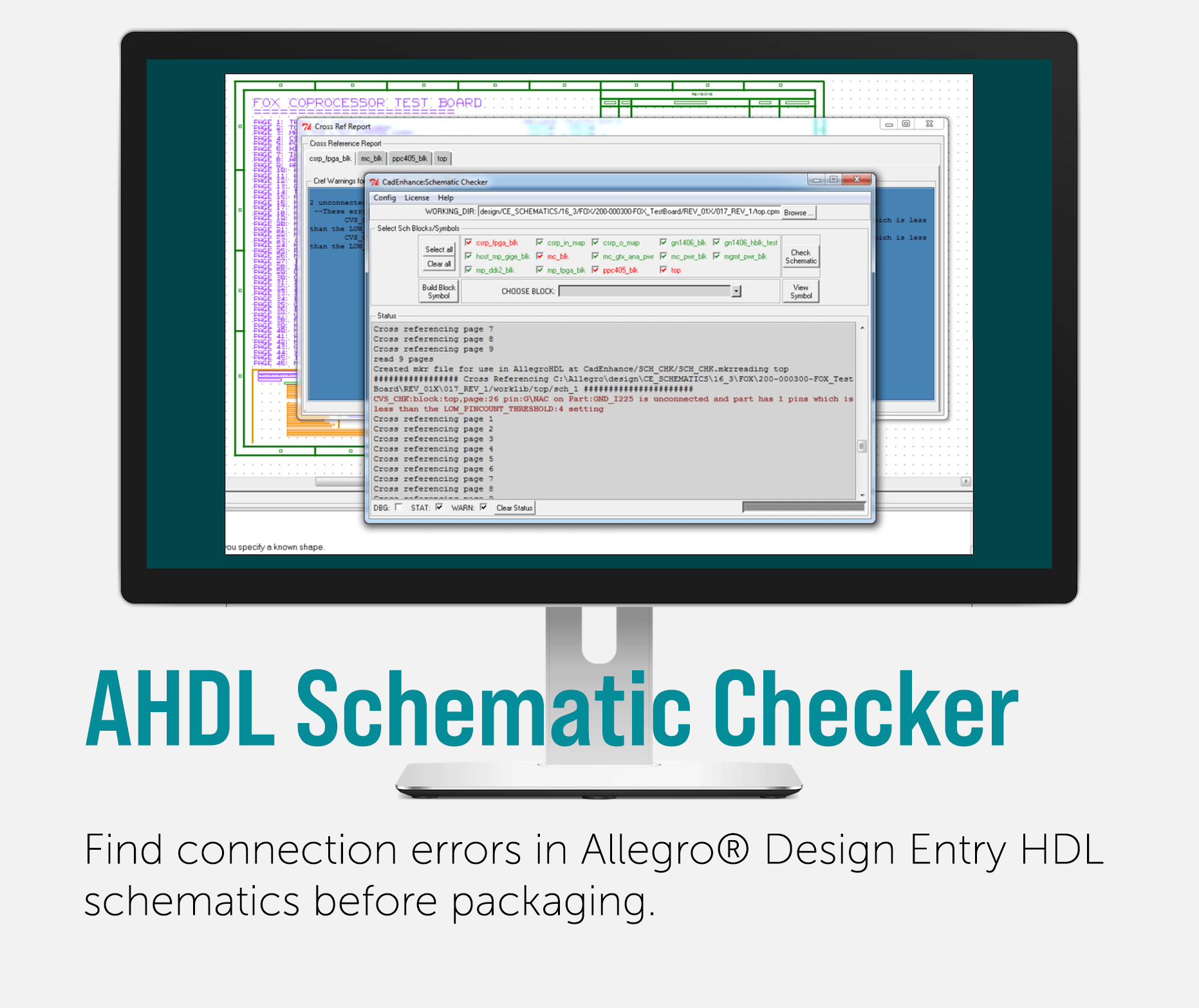

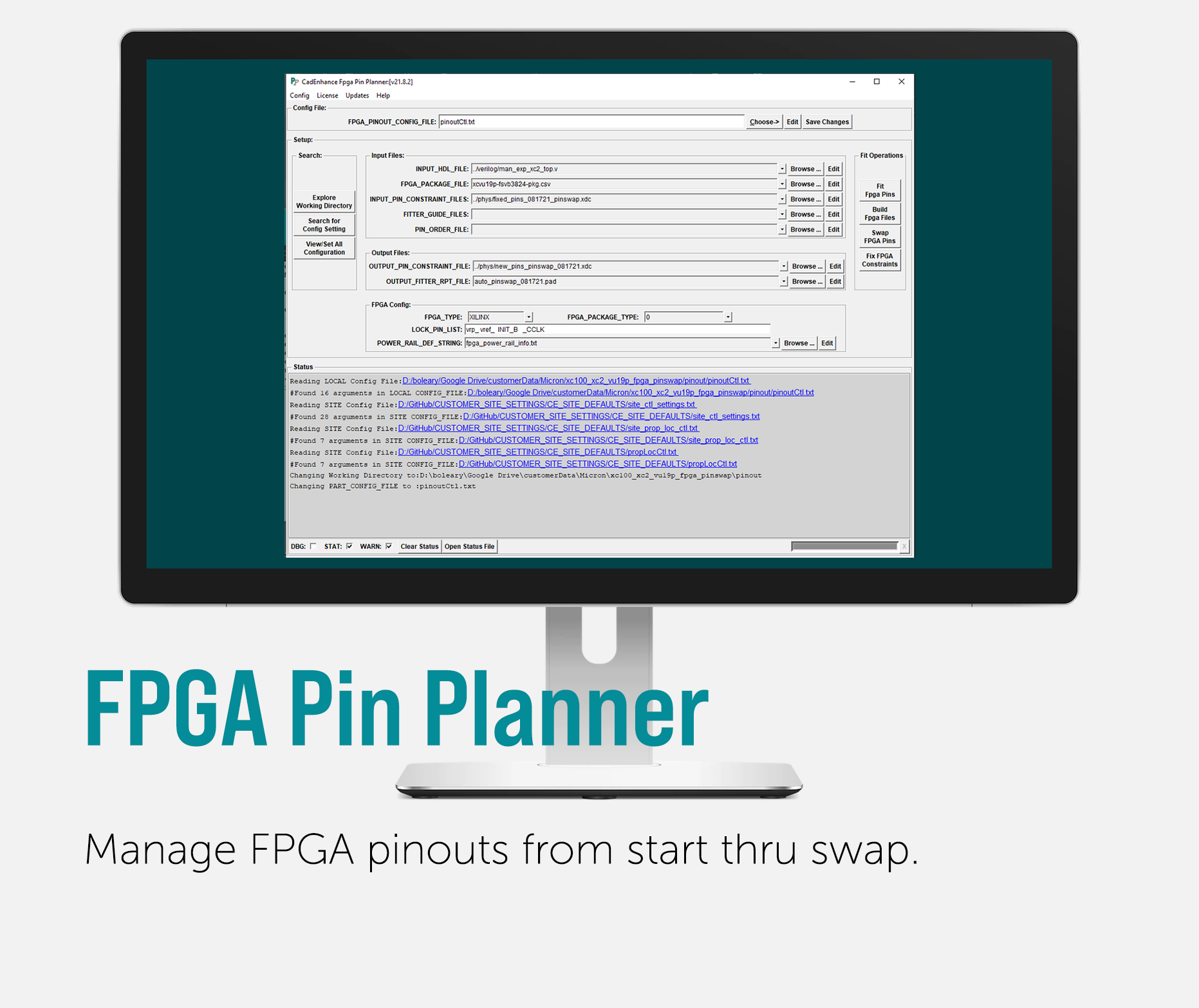

Increase the accuracy and efficiency of your hardware design flows in Cadence® Allegro® Design Entry HDL, Cadence® Capture®, Altium®, Mentor Graphics® and Zuken® Design Gateway Schematic tools with our time saving add-ons.

Click on a tool’s Image to visit the related product page