How to Build IBIS Models for Intel® AgileX® FPGA Designs

IBIS models give hardware designers the ability to run Signal Integrity Simulations to visualize and optimize the expected performance of device to device interconnects as implemented in their PCB. Designers use board simulation tools like Hyperlynx® from Siemens®, Sigrity® from Cadence®, ADS® from KeySight®, and HSpice® from Synopsys® with IBIS Models to run their simulations.

If you are reading this, you are probably not new to IBIS Models, but just in case, here is some great background information on IBIS files from Qualcomm®.

Most IC vendors provide a detailed IBIS model for their specific devices, but FPGA devices are tricky because each I/O bank pin needs to be assigned the proper model in accordance with how it is used in the target design. The I/O driver selected for each FPGA Pin can be configured differently to improve performance on the board and the user needs to be able to simulate the effects of the final configuration for that every pin.

FPGA vendors like Intel®, Xilinx®, Lattice® and MicroChip® provide tools to create a design specific IBIS model, but support for these tools sometimes lags behind the release and delivery of the actual device in the design software. Intel’s Latest AgileX devices fall into that case. The creation of design specific IBIS model for these new giant FPGA devices, some with >3000 pins, are not yet supported by the Intel Quartus Tool.

See This Intel® Community Discussion: Generating an Agilex per pin RLC IBIS File which details the steps required to get the job done manually.

CadEnhance had some internal IBIS model generation tools, but we hadn’t released them publicly as an available toolset. Working with an Intel® Applications Engineer, we quickly tweaked our tools to work with the data that Intel provides on their IBIS Models for Intel FPGA Devices Page. Our clever intern Jiading Li added the capability to create the design specific IBIS models to our FpgaPinPlanner Tool.

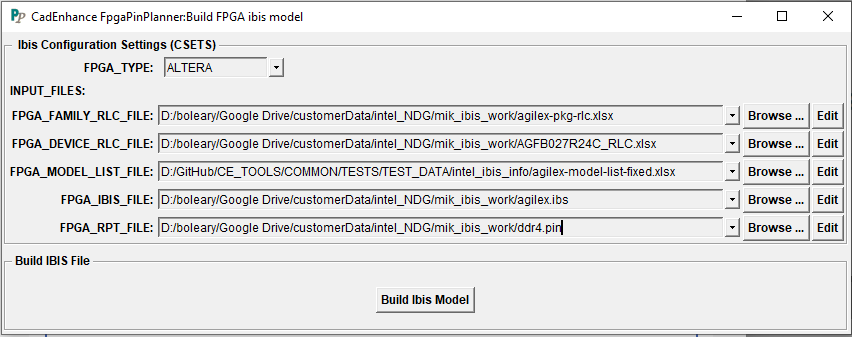

IBIS model Builder GUI in FpgaPinPlanner.

How it works

You download 3 spreadsheets and the sample Agilex.ibs file from the IBIS Models for Intel FPGA Devices Page.

Note that you may need to request the FPGA_DEVICE_RLC_FILE directly from Intel PSG support because they are not freely published on the website. You can build without this file, but your model accuracy will suffer.

FpgaPinPlanner reads the 2 package spreadsheets from and extracts pin and package RLC parameters for the selected device.

It reads the sample Agilex.ibs file which contains one pin for each I/O Standard supported by the AgileX devices and all of the I/O model data.

It also reads the Intel® AgileX® Model List Spreadsheet to create IBIS model selectors for each supported I/O Standard and Pin Type combination

Finally, it reads the design.pin file produced by Quartus® which contains the pin name, pin number, pin direction and configured I/O standard for each pin in the customer’s design.

With all that information in hand, FpgaPinPlanner merges it all into the device specific IBIS model.

Component and Pin Section

A line for each device pin is added with the appropriate model selector for the I/O Standard and pinType used in your design, and the RLC parameters for the package pin.

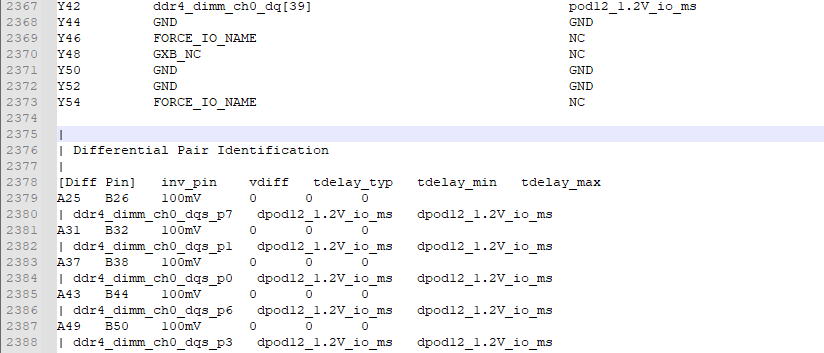

Automatic Differential Pair Identification

FpgaPinPlanner automatically identifies the differential pairs present in the input pin data and creates the individual [Diff Pin] Definitions used by the simulation tools:

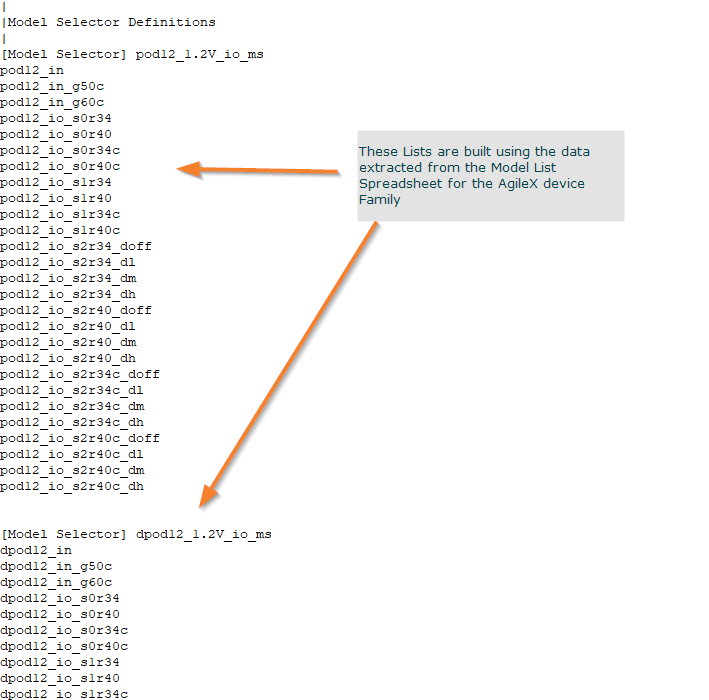

Model Selectors

The Model Selectors lists are added with one model selector for each unique combination of I/O standard and pinType used in the FPGA design. The use of Model Selectors is key to allow users to interactively select different models in the simulation environment. This allows the designer to choose the proper parameters for a selected I/O pin in order to get optimal signal integrity performance in the target board.

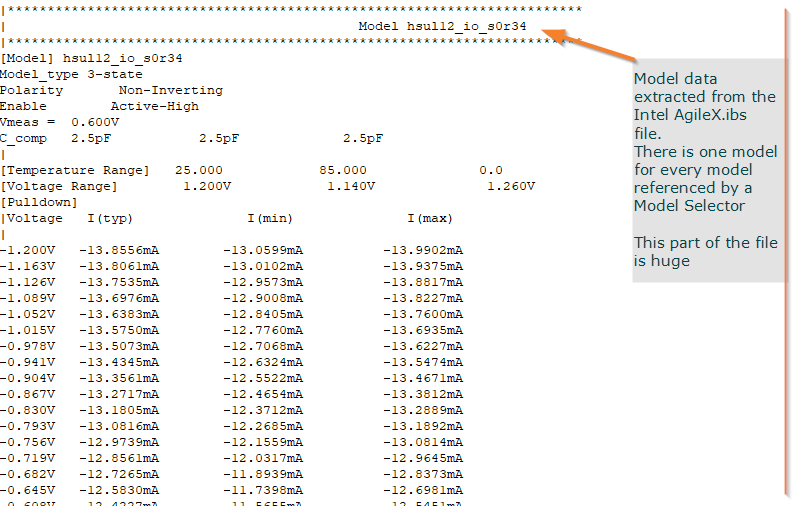

Model Data

Finally FpgaPinPlanner adds the model data extracted from the sample Agilex.ibs file for every model referenced by a model_selector.

Try it for free on your design

Enter your email below to get the link to download FpgaPinPlanner. After you install it, we’ll send you a key to use all of the features free for 30 days which should get your simulations started with no risk at all.

As a bonus, the download includes our incredible Free Symbol Viewer and access to our FREE CE-HDL features.